Broadwell Xeon E5-2600 v4 - bliskie spotkanie z najnowszymi procesorami od Intel

Intel oficjalnie wprowadził na rynek swoje lekko spóźnione procesory Xeon E5 v4.

To kolejna odsłona linii Xeon, której wersja E5 v3 z 2014 roku charakteryzowała się wielkością 22nm i wykorzystywała mikroarchitekturę Haswell. Intel zmniejszył Haswell do 14nm, co po wprowadzeniu kilku innych zmian zakończyło się stworzeniem rozwiązania o kodowej nazwie Broadwell.

Procesory umieszczane w serwerach i stacjach roboczych wykorzystywały elementy architektury Broadwell już w 2015 roku. Teraz pora, aby światło dzienne ujrzały oparte na Broadwell procesory Xeon E5 v4 skierowane do użytku w maszynach typu scale-out.

Xeon E5-2600 v4 - charakterystyka

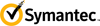

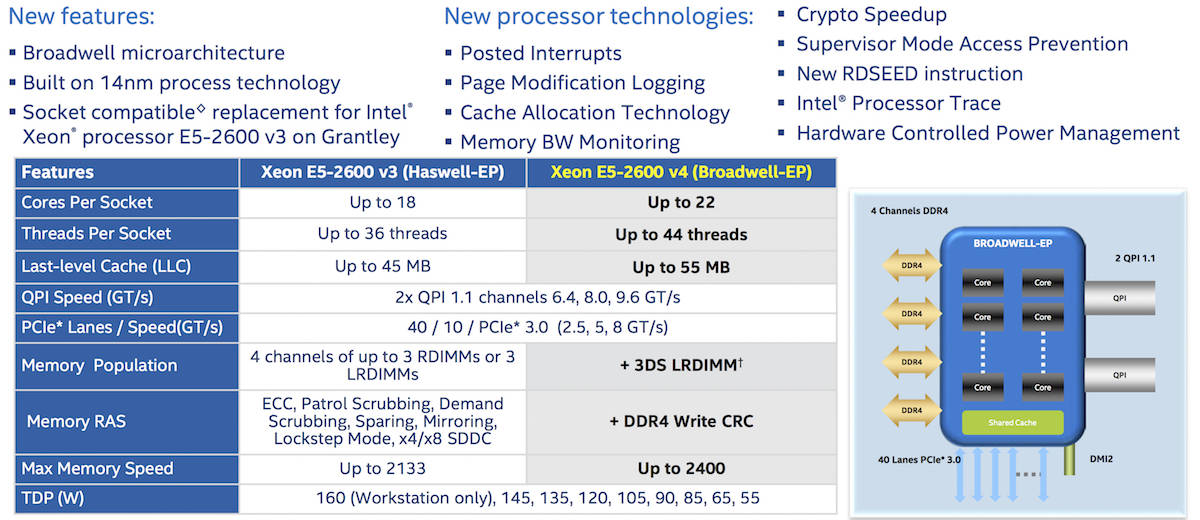

Poniżej przedstawiamy podsumowanie nowej linii Xeon E5 v4 wraz z porównaniem do poprzedników z linii v3. Nowości od Intel mogą posiadać do 22 rdzeni, do 44 wątków na gniazdo, do 55MB LLC (last-level cache znany także jako L3), wspierać 2400 MHz RAM i DDR4 write CRC. Każdy rdzeń posiada 2KB data cache typu L1, 32KB instruction cache L1 i 256KB cache typu L2.

Dodatkowe rdzenie będące wyrazem niezwykłego wyrafinowania projektantów architektury stanowią, dzięki swoim zmniejszonym rozmiarom, to co daje Broadwell przewagę nad Haswell.

Przykładowy przedstawiciel linii - dwugniazdowy Xeon E5-2600 v4 w wersji 14C wyposażony jest w 14 rdzeni i zegar o prędkości 2.4GHz. Jeśli użytkownicy oczekiwali po nowych procesorach odświeżenia sprzętu na pewno się nie zawiodą. Rozwiązania Xeon E5 v4 są także kompatybilne z gniazdami procesorów E5 v3 Grantley.

Po krótkiej charakterystyce pora na trochę szczegółów.

Jak ułożone są rdzenie

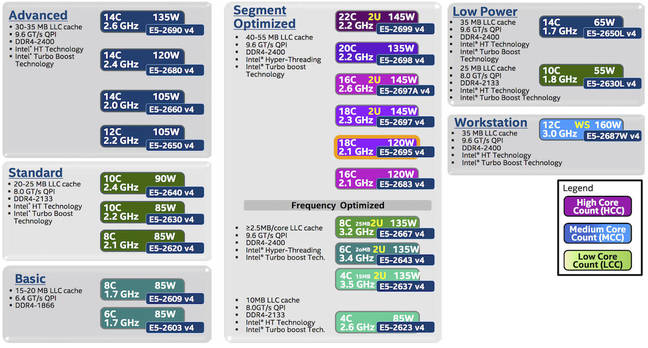

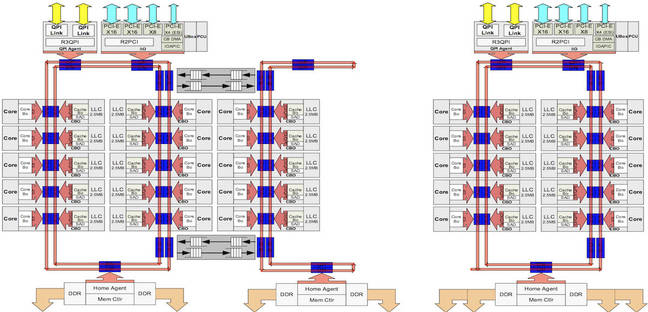

Tak jak było to w przypadku Haswell, w architekturze Broadwell wykorzystano symetryczny, zbliżony do okręgu układ elementów mający ułatwić efektywne połączenie fizycznych rdzeni z cache i światem zewnętrznym. W wersjach o największej ilości rdzeni – choćby tej z 22 rdzeniami i 7,2 mld tranzystorów, procesor posiadana dwa niezależne pierścienie połączone w dwóch miejscach. Jeden z pierścieni odpowiedzialny jest za komunikację z QPI i interfejsami PCIe gen-3, natomiast oba posiadają własne kontrolery RAM, z który każdy wspiera dwa kanały.

Cache typu LLC jest podzielony na części. Każda z nich jest podłączona to pierścienia w miejscu przeciwległym to ułożenia rdzenia. Gdy rdzeń uzyskuje dostęp do pamięci, wybrany adres fizyczny jest przetwarzany umożliwiając lokalizację cache w pierścieniu. Elementy cache L3 na pierścieniu nie są umieszczone naprzeciwko rdzenia, zamiast tego mogą one przechowywać dane dla wielu innych rdzeni. Wykorzystywany algorytm pozwala Intel na równomierną dystrybucję żądań dostępu do pamięci na przestrzeni całej struktury. Prawdopodobnie potrzeba nawet do 12 cykli wokół okręgu, aby żądanie cache trafiło do odpowiedniego elementu. W większości przypadków proces ten ma trwać o wiele krócej i wymagać nie więcej niż kilku cykli.

Inżynierowie Intel nie ujawniają szczegółów algorytmu, aby uniemożliwić wprowadzanie zmian w systemie poprzez przekształcenia jądra zapewniające rdzeniom bezpośredni dostęp do fizycznej pamięci znajdującej się najbliżej danego elementu cache, minimalizując tym samym minimalne opóźnienia wynikające z opisanych wyżej cykli wokół pierścienia.

Poniżej prezentujemy dwupierścieniowy system oraz rozwiązanie zastosowane przez Intel w procesorach z mniejszą ilością rdzeni.

Zmiany w mikroarchitekturze

Intel twierdzi, że wydajność pojedynczego wątku w zakresie wykonanych w ciągu sekundy instrukcji jest w architekturze Broadwell o 5% wyższa niż w przypadku Haswell. Osiągnięcie takiego wyniku było możliwe dzięki wielu usprawnieniom.

Latencja instrukcji MULPS i MULPD została zredukowana z pięciu do trzech cykli. Podobnie ograniczono ją w DIVSS, DIVSD, DIVPS i DIVPD. Przykładowo, 256-bitowy wektor liczb pojedynczej precyzji charakteryzuje się latencją na poziomie 16 cykli, która w Haswell wynosiła 20 cykli. Podziały skalarne mogą być rozłożone na dwie części i równolegle przetwarzane.

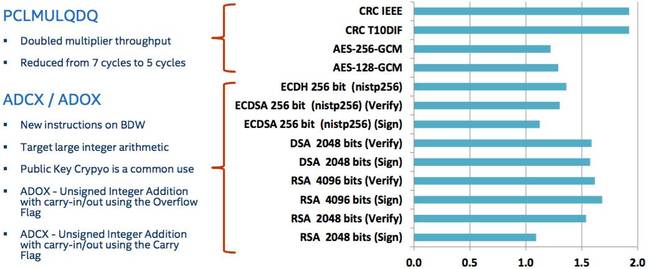

Instrukcje ADC, CMOV i PCLMULQDQ (ostatnia wykorzystywana w szyfrowaniu AES) także przyśpieszyły. Podniesiono efektywność buforów TLB zwiększając STLB z poziomu 1000 do 1500 wejść. Poprawiono także przewidywanie adresu. Architektura Broadwell pełna jest tego typu drobnych usprawnień ułatwiających efektywne kodowanie.

Lepsze wykorzystanie energii przy obsłudze zmiennych obciążeń

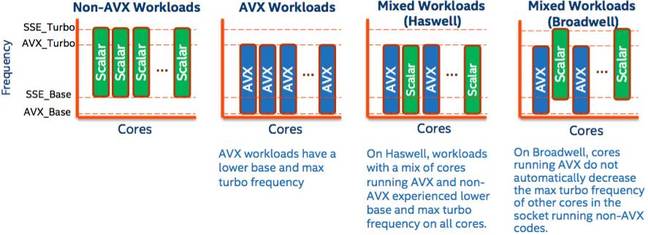

Instrukcje AVX od Intel mają tendencję do podnoszenia ilości energii zużywanej przez procesor, w związku z czym zmuszony jest on zmniejszyć częstotliwość zegara, aby zapobiec własnemu przegrzaniu. Poprzednio, gdy rdzeń procesora Intel rozpoczynał działania na kodzie AVX obniżana była częstotliwość wszystkich rdzeni. W Broadwell rdzenie nie obsługujące kodu AVX nie są spowolniane i mogą pracować normalnie. Oznacza to, że procesor może obsługiwać jednocześnie dwa typy obciążeń bez ponoszenia dodatkowych kosztów.

Gdy rdzeń nie obsługuje żadnych operacji AVX przez określony czas – około milisekundy – spowolnienie częstotliwości zegara zostanie zatrzymane. W przypadku użytkowników, których serwery obsługują ogromne ilości operacji bazujących na AVX zaobserwowanie zmian w tym zakresie może być niezwykle trudne.

Przyśpieszenie szyfrowania

Intel twierdzi, że był w stanie przyśpieszyć w Broadwell kodowanie AES, a także podpisywanie i weryfikację ECDSA, RSA i RSA poprzez redukcję PCLMULQDQ z siedmiu do pięciu cykli oraz wprowadzanie nowych instrukcji użytecznych w algorytmach szyfrowania. Dwie nowe instrukcje to ADOX i ADCX. Serwery wykorzystujące najnowsze procesory Intel wraz z dodatkowymi instrukcjami będą miały ułatwione zadania szyfrowania, deszyfrowania i weryfikacji danych.

Wykresy pokazują porównanie prędkości 8-rdzeniowego Broadwell Xeon-D wyposażonego w 2x8GB RAM i 18-rdzeniowego Haswell Xeon E5-2699 v3 z 4x32GB RAM podczas testów szyfrowania z wykorzystaniem OpenSSL-1.0.2-beta3 na Linux. Przykładowo, Xeon Broadwell wykonał operację weryfikacji RSA przy użyciu 2048-bitowego klucza 1,5 razy szybciej niż jego kuzyn z linii Haswell.

Do dyspozycji jest także RDSEED, który może być wykorzystywany jako generator liczb pseudolosowych (PRNG) o wartościach losowych, kluczowych dla silnego szyfrowania. Warto w tym momencie wspomnieć, że dla użytkowników, którzy nie są fanami instrukcji RDRAND ze względu na jego budowę typu black box, opcja RDSEED także nie będzie idealnym rozwiązaniem.

Broadwell wprowadza także opcję Supervisor Mode Access Prevention (SMAP). Pozwala ona jądru systemu na ustawienie flagi w rejestrze kontrolnym (CR4), aby zablokować dostęp kodów typu kernel-mode do pamięci w trybie użytkownika. Zapobiega to niespodziewanym manipulacjom aplikacjami – przypadkowym lub złośliwym – ze strony zaufanych kodów typu low-level. Jądro może przełączyć flagę wyłączając czasowo tę opcję w momencie, w którym dostęp do określonych zasobów jest konieczny.

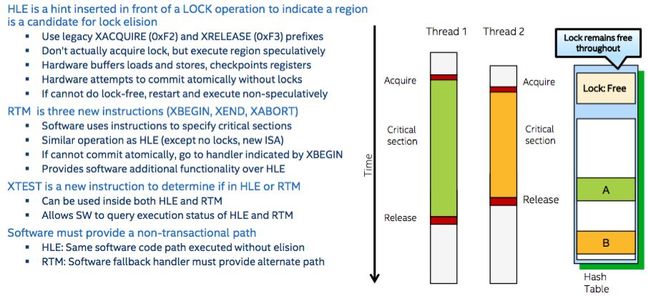

Warto wspomnieć o powrocie Rozszerzeń Synchronizacji Transakcyjnej (TSX) zastosowanych także w Xeon E5 v4, które poprzednio wycofano z użycia po stwierdzeniu znaczącej ilości awarii.

TSX pozwala programistom wyróżniać początek i koniec krytycznych części kodu współdzielonego i monitorować dostępy pamięci podczas pracy w danych obszarach. Zapisy i odczyty do i z pamięci są przekierowywane do buforów sprzętowych. Na końcu danej sekcji krytycznej, dane przypisywane są do RAM.

Jeśli dwa wątki starają się manipulować tymi samymi danymi w tym samym czasie w ramach określonej sekcji, bufory są usuwane, a wątki przywracane do początku sekcji. Następnie jeden z wątków jest zatrzymywany, podczas gdy drugi samodzielnie przemieszcza się przez sekcję krytyczną.

Jeżeli z kolei wątki pracują na tej samej strukturze danych, ale w innych jej częściach nie wchodząc sobie tym samym w drogę nie ma potrzeby ich powstrzymywania: procesor traktuje pracę każdego z wątków jak odrębne działanie. Deweloperzy mogą wykorzystywać do wyznaczania sekcji krytycznych rozwiązania Restricted Transactional Memory (RTM) lub Hardware Lock Elision (HLE).

Dzięki unikaniu stosowania blokad, bazy danych mogą szybciej przetwarzać operacje, a aplikacje nie marnują czasu i energii na niepotrzebne działania. Biorąc pod uwagę złożoność wszystkich procesów, nie dziwi czas jaki zajęło Intel dopracowanie wszystkich szczegółów tej technologii.

Kontrola cache

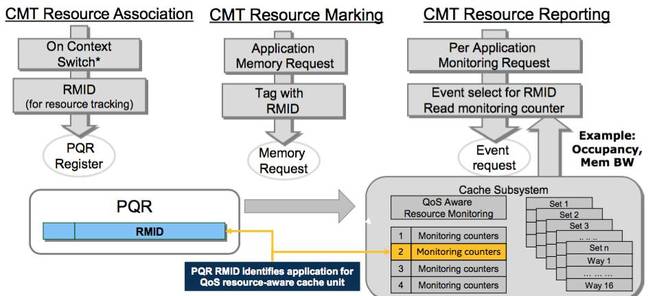

Intel ma w ofercie także zestaw funkcjonalności znanych pod wspólnym określeniem Resource Director Technology. Jednym zdaniem pozwalają one systemowi operacyjnemu na monitorowanie wykorzystanego przez software cache. Wątki, procesy i całe wirtualne maszyny mogą uzyskać przypisane przez system operacyjny Resource Monitoring ID (RMID). Kiedy dany wątek ma rozpocząć działanie, jądro systemu uzyskuje jego RMID i wpisuje je do specjalnego rejestru, odpowiedniego dla każdego rdzenia (IA32_PQR_ASSOC znanego także jako PQR). Podczas trwania działania wątku uzyskuje on dostęp do każdej jednostki pamięci wykorzystując RMID w PQR.

Później jądro systemu może pozyskać z procesora telemetrię danego RMID, dzięki czemu możliwe jest odczytanie chociażby poziomu obłożenia cache L3. Procesory Broadwell wspierają dwa razy więcej RMID niż rdzenie Haswell. Mogą także monitorować przepustowość pamięci.

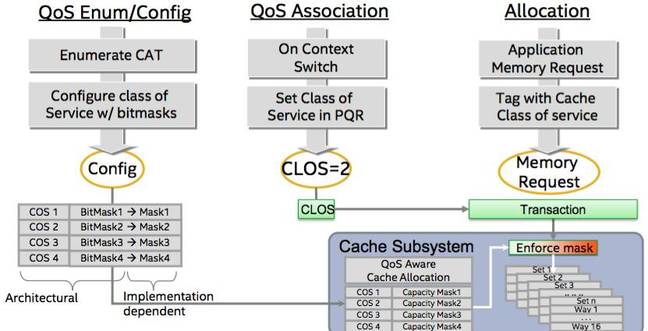

Innym elementem tego rozwiązania jest opcja Classes of Service (CLOS). Jądro może zaprogramować w ramach procesora zestaw klas quality-of-service (QoS), z której każda z nich definiuje poziom obciążenia cache. Przy okazji każdego przełączania zadania, jądro przypisuje do mającego działać w następnej kolejności wątku, procesu lub wirtualnej maszyny ID danej klasy przy użyciu rejestru PQR. Gdy wątek uzyskuje dostęp do pamięci, procesor wykorzystuje jego ID i sprawdza limity obłożenia korespondującego z nim cache odpowiedniej klasy. Następnie określony limit jest stosowany, aby zatrzymać dany wątek lub proces przed awarią, np. zapętleniem kopiowania w cache L3 i wymazaniu innych danych.

Zmiany w wirtualizacji

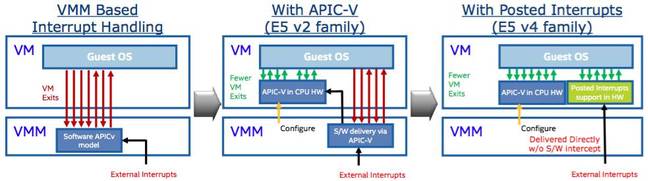

Xeon E5 v4 wyposażony został w dodatkową funkcjonalność, tzw. wyzwolone przerwania. Pozwalają one hypervisorowi na przekierowanie przerwań sprzętowych bezpośrednio do maszyny wirtualnej. Zazwyczaj w momencie rozpoczęcia przerwania maszyna wirtualna jest zmuszona do zatrzymania się, a hypervisor przejmuje inicjatywę w zakresie żądania hardware’u – odsunięcie się maszyny jest czasochłonną operacją trwającą kilkaset cykli procesora. Następnie hypervisor musi sam zająć się samym przerwaniem lub przydzielić to zadanie maszynie wirtualnej.

Wyzwolone przerwania pozwalają hypervisorowi na takie zaprogramowanie procesora, aby przerwania przechodziły bezpośrednio przez maszynę wirtualną bez konieczności "wychodzenia" do hypervisora. Mogą być one także ustawione w taki sposób, by pracująca maszyna wirtualna skończyła wykonywanie priorytetowych zadań w czasie kiedy inna maszyna zostaje przypisana do obsługi przerwania. Oznacza to, że hypervisor może uniknąć przełączania między maszynami za każdym razem, gdy przerwanie ma miejsce.

Zalety tego rozwiązania są oczywiste: maszyny wirtualne mogą reagować znacznie szybciej na jakiekolwiek problemy sprzętowe, zwiększając wydajność w ramach wrażliwych na opóźnienia zadań. Dla Intel wyzwolone przerwania są niezbędnym elementów systemów Network Functions Virtualized (NFV), które przesuwają obciążenia typu computer networking z hardware’u na software. Maszyna wirtualna odpowiedzialna za tzw. packet switching musi być zdolna do natychmiastowej reakcji na nadchodzące przerwanie i nie może czekać aż hypervisor zatrzyma ją, przeprocesuje przerwanie i wznowi jej działanie. Dzięki wyzwolonym przerwaniom maszyna otrzyma powiadomienie od hardware’u bez konieczności czasowego usuwania się z całego procesu.

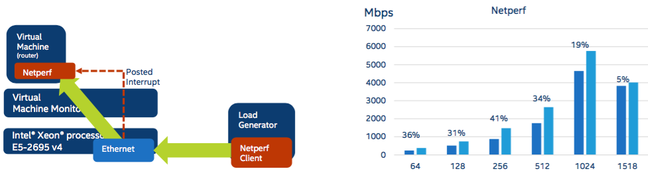

Intel twierdzI, że wykorzystując w testach wyzwolone przerwania do przesyłania przerwań karty ethernet bezpośrednio do maszyny wirtualnej, ilość przesuniętych danych była o 41% większa niż w przypadku korzystania z systemu nie posiadającego tej opcji. Taki wynik osiągnięto z wykorzystaniem 256-bajtowych pakietów. Działanie na pakietach 1KB przyniosło poprawę o 19%.

Szczegółowy opis wyzwolonych przerwań został opisany w tej instrukcji Intel [sekcja 5.2.5].

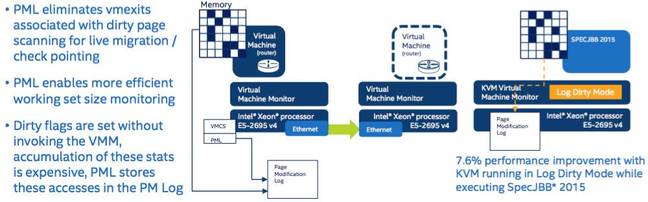

Innym usprawnieniem w zakresie wirtualizacji jest Page-Modification Logging. W momencie, w którym oprogramowanie modyfikuje strony pamięci, procesor umieszcza w tabelach stron w strukturze systemu informacje o wejściach danej strony. Dzięki tej funkcji wiadomo jakie strony zapisać na dysk przy wymianie, a także które przesłać z jednej maszyny do drugiej w przypadku migracji pracującej aplikacji.

Ten rodzaj dodatkowych zapisów pozwala na szybkie i bezbolesne przeniesienie danych stron z jednego serwera na drugi, przy zachowaniu w pełni działającego programu.

Przechodzenie przez wszystkie tabele stron i sprawdzanie określonych powyżej zapisów jest zadaniem jądra systemu lub hypervisora, zwłaszcza w trakcie migracji na żywo. Page-Modification Logging od Intel utrzymuje w pamięci wpisy dotyczące zmienionych stron, dzięki którym ich dokładnie przeanalizowanie jest szybsze niż w przypadku standardowych struktur danych.

Intel stara się jak najlepiej opracować technologię migracji na żywo uznając to za konieczny element NFV. Jednym z najmocniejszych punktów sieci typu software-defined jest ich zdolność do przenoszenia i skalowania obciążeń zgodnie z potrzebami. Jeśli migracja trwa zbyt długo, klient branży telekomunikacyjnej może zacząć zastanawiać się, dlaczego ma pozbyć się dedykowanego sprzętu na rzecz standardowych serwerów, które potencjalnie oferują większą elastyczność, ale nie są w stanie nadążyć z działaniem.

Dodatkowe opcje

Linia Xeon E5 v4 będzie wyposażona w Hardware Controlled Power Management, funkcję odbierającą systemowi operacyjnemu zadanie zarządzania energią i przekazującą ją procesorowi. Istnieje możliwość konfiguracji tego rozwiązania, a także całkowitego wyłączenia. System może także przekazywać procesorowi wskazówki dotyczące prawidłowego bilansowania zużycia energii

i wydajności.

Xeon E5 v4 to także rozwiązanie Processor Trace umożliwiające zaawansowane debugowanie: możliwe jest pisanie do pamięci pakietów opisujących objęte przez oprogramowanie obszary i napotkane zdarzenia, a także filtrowanie procesu śledzenia poprzez wskaźnik kontroli zapisu CR3 lub rodzaj wykorzystanego trybu pracy. Zainteresowani tego typu rozwiązaniami deweloperzy na pewno znajdą coś dla siebie.

Mimo pewnych wątpliwości związanych z różniącymi się w zależności od producenta benchmarkami, przedstawiamy poniżej wykres opublikowany przez Intel porównujący Xeon E5-2699 v4 z E5-2699 v3.

Pokazuje on wzrost wydajności v4 Broadwell wobec v3 Haswell o ok. 20% w zależności od rodzaju testu, przy porównaniu wersji 22-rdzeniowej do opcji wyposażonej w 18 rdzeni. Wiele z wymienionych wyżej funkcji było podanych do publicznej wiadomości po raz pierwszy w zeszłorocznych prezentacjach części architektury Broadwell, a nawet w wersji Haswell. Linia E5-2600 v4 korzysta z ogromnej większości wprowadzonych w mikroarchitekturze ulepszeń i umożliwia korzystanie z nich serwerom typu scale-out, czyli maszynom budującym rozwiązania chmurowe i sieci typu software-defined.

Podsumowaniem nowej rodziny E5-2600 może być jedno zdanie: to kolejny Xeon. Wystarczy włożyć go do maszyny i podłączyć do internetu. Nie narzuca się, jest nieszkodliwy. Jest lepszy od rozwiązań dostępnych 2 lub 3 lata temu i to wystarczy, aby zwrócić uwagę zarządzających systemami IT, którzy szukają sposobu na odświeżenie swoich rozwiązań, a także zachęcić deweloperów funkcjonalnościami takimi jak TSX czy instrukcje wspierające efektywne szyfrowanie. Tak naprawdę nie musi robić wiele więcej. Tak wygląda rzeczywistość, gdy do marki należy 99% rynku procesorów data center.

Produkt został dodany do zapytania.

Produkt został dodany do zapytania.